# SAT-based Formal Verification of Fault Injection Countermeasures for Cryptographic Circuits\*

Huiyu Tan<sup>1,2</sup>, Pengfei Gao<sup>3</sup>, Fu Song<sup>4,5</sup> (⋈), Taolue Chen<sup>6</sup> and Zhilin Wu<sup>4</sup>

Shanghai Tech University, Shanghai 201210, China

Wingsemi Technology Co., Ltd., Shanghai 201203, China

Bytedance, Beijing 100098, China

<sup>4</sup> Key Laboratory of System Software (Chinese Academy of Sciences) and State Key Laboratory of Computer Science, Institute of Software, Chinese Academy of Sciences, Beijing 100190, China, songfu@ios.ac.cn

Nanjing Institute of Software Technology, Nanjing 211135, China Birkbeck, University of London, WC1E 7HX, UK

**Abstract.** Fault injection attacks represent a type of active, physical attack against cryptographic circuits. Various countermeasures have been proposed to thwart such attacks, however, the design and implementation of which are intricate, error-prone, and laborious. The current formal fault-resistance verification approaches are limited in efficiency and scalability. In this paper, we formalize the fault-resistance verification problem and show that it is coNP-complete. We then devise a novel approach for encoding the fault-resistance verification problem as the Boolean satisfiability (SAT) problem so that modern off-the-shelf SAT solvers can be utilized. The approach is implemented in an open-source tool FIRMER which is evaluated extensively on realistic cryptographic circuit benchmarks. The experimental results show that FIRMER is able to verify fault-resistance of almost all (72/76) benchmarks in 3 minutes (the other three are verified in 35 minutes and the hardest one is verified in 4 hours). In contrast, the prior approach fails on 31 fault-resistance verification tasks even after 24 hours (per task).

**Keywords:** Fault Injection · Cryptographic Circuits · SAT · Formal Verification

#### 1 Introduction

Cryptographic circuits have been widely used in providing secure authentication, privacy, and integrity, due to rising security risks in sensor networks, healthcare, cyber-physical systems, and the Internet of Things [AIM10, TS21, NIS22]. However, cryptographic circuits are vulnerable to various effective physical attacks, which remains an open challenge even after two decades of research. This paper focuses on an infamously effective attack, i.e., fault injection attacks [BS97, BDF<sup>+</sup>14, BHL17, Bak22].

Fault injection attacks deliberately inject disturbances into a cryptographic circuit when it is running cryptographic computation, and analyze the information from the correct (nonfaulty) and the incorrect (faulty) outputs, attempting to deduce information on the secret key. Fault injection attacks allow the adversary to bypass certain assumptions in classical cryptanalysis methods where the cipher is considered to be a black box and therefore cannot

<sup>\*</sup>This work was funded by the Strategic Priority Research Program of CAS (XDA0320101), National Natural Science Foundation of China (62072309), CAS Project for Young Scientists in Basic Research (YSBR-040), ISCAS New Cultivation Project (ISCAS-PYFX-202201), ISCAS Fundamental Research Project (ISCAS-JCZD-202302), an overseas grant from the State Key Laboratory of Novel Software Technology, Nanjing University (KFKT2023A04).

be tampered. The disturbances could be injected in various different ways, such as clock glitches [ADN+10, ESH+11, SHO19], underpowering [SGD08], voltage glitches [ZDCT13], electromagnetic pulses [DDRT12, DLM19, DLM21] and laser beams [SA03, RSDT13, CLFT14, SFG+16, DBC+18]. Secret information can be deduced by differential fault analysis [BS97], ineffective fault analysis [Cla07a], statistical fault analysis [FJLT13], and statistical ineffective fault analysis [DEG+18]. Therefore, fault injection attacks pose a severe security threat to embedded computing devices with cryptographic modules.

Both detection-based and correction-based countermeasures have been proposed to defend against fault injection attacks [MSY06, AMR<sup>+</sup>20, SRM20]. The former aims to detect fault injections and infect the output result with an error flag in the presence of faults so an attacker cannot exploit them; the latter aims to correct the faulty cryptographic computation in the presence of faults. An effective countermeasure must be *fault-resistance*, i.e., detecting or correcting faults in time once they occur. Designing and implementing secure, efficient, and low-cost cryptographic circuits is notably error-prone, hence it is crucial to rigorously verify fault-resistance, especially at the gate level (which is closer to the final circuit sent to the fab for the tape-out). Typically this is done at the last stage of the front-end design so the flaws introduced by front-end tools (e.g., optimization passes) can be detected.

There is more specialized work for assuring fault-resistance, (e.g., [SKK13, BGE<sup>+</sup>17, SMD18, AWMN20, KRH17, SSR<sup>+</sup>20, WLR<sup>+</sup>21, NOV<sup>+</sup>22]), but almost all of them focus on finding flaws or checking the effectiveness of user-specified instances (given by fault test vectors). In principle, to achieve completeness, all the possible test vectors (varying in fault types, injected gates, and clock cycles) must be checked under all valid input combinations, which is virtually infeasible in practice, as already recognized, e.g., by [RBSS<sup>+</sup>21]. To alleviate this issue, recently, a binary decision diagram (BDD) [Bry86] based approach, called FIVER [RBSS<sup>+</sup>21], was proposed, which does not need to explicitly enumerate all valid input combinations and is optimized to avoid some fault test vectors. However, it still has to repeatedly build BDD models for a huge number of fault test vectors, failing to verify relatively larger circuits in a reasonable amount of time. (For instance, it fails to prove fault-resistance of a single-round 2-bit protected AES in 24 hours.)

Contributions. In this work, inspired by the consolidated fault model for precisely defining fault injection adversaries [RBSG23], we define a fault-resistance model as  $\zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$ , where  $\mathbf{n}_e$  specifies the maximum number of fault events per clock cycle,  $\mathbf{n}_c$  specifies the maximum number of clock cycles in which fault events can occur, T specifies the set of allowed fault types including bit-set, bit-reset and bit-flip; and  $\ell$  specifies the types of gates that can be faulted including logic gates in combinational circuits and memory gates.

Note that, as in [RBSG23, RBSS+21], we focus on transient fault events that are of a dynamic nature and become inactive after certain periods or changes in the circuit. More precisely, each fault event is accompanied with the clock cycle of the fault injection. There are persistent and permanent fault events which are of a static nature and will remain active for several or even the entire clock cycles. As remarked by [RBSS+21], the latter two can be modeled as repetitive transient fault events, thus are not explicitly considered in the fault-resistance model. Moreover, following [RBSG23, RBSS+21], we assume that the adversary can precisely control fault injections, consequently, fault-resistance against random faults can be achieved as they can be encoded by fault vectors and our verification approach covers all the feasible fault vectors. We formalize the fault-resistance verification problem using the fault-resistance model which is shown to be coNP-complete. This lays a solid foundation for the subsequent verification.

We propose novel SAT-based approaches for verifying fault-resistance. Technically, with

<sup>&</sup>lt;sup>1</sup>In the computational complexity theory, coNP is the class of problems the complement of which are in NP, where NP is the class of problems which can be solved in polynomial-time by a nondeterministic Turing machine.

a countermeasure and a fault-resistance model, we generate a new conditionally-controlled faulty circuit, which is in turn reduced to the SAT problem. Intuitively we replace each vulnerable gate with a designated gadget (i.e., sub-circuit) with (1) a control input for controlling if a fault is injected on the gate, and (2) selection inputs for choosing which fault type is injected. This approach avoids explicit enumeration of all the possible fault test vectors and can fully utilize the conflict-driven clause learning (CDCL) feature of modern SAT solvers. Furthermore, we introduce a reduction technique to safely reduce the number of vulnerable gates when verifying fault-resistance, which significantly improves the verification efficiency.

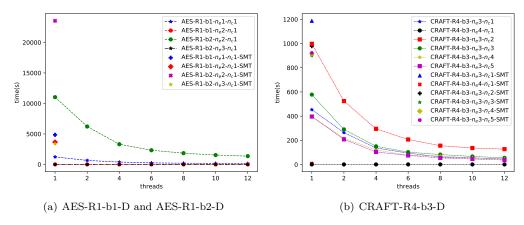

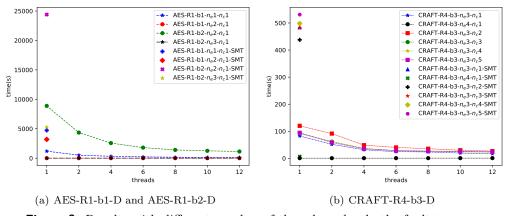

We implement our approach in an open-source tool FIRMER (Fault Injection counteR Measure verifiER), based on Verilog gate-level netlists. We evaluate FIRMER on 33 realistic cryptographic circuits (i.e., rounds of AES, CRAFT, LED, GIFT, PRESENT and SIMON) with both detection- and correction-based countermeasures, where the number of gates ranges from 608 to 68,703. The results show that our approach is effective and efficient in verifying the fault-resistance against various fault-resistant models. Almost all the benchmarks (72 out of 76) can be verified in less than 3 minutes (except for three which take 35 minutes and one which takes 4 hours). In comparison, FIVER runs out of time (with timeout 24 hours) on 31 fault-resistance verification tasks in the same setting. To summarize, we make the following major contributions:

- We formalize the fault-resistance verification problem and identify its coNP-complete computational complexity for the first time.

- We propose a novel SAT-based approach for formally verifying fault-resistance with an accelerating technique.

- We implement an open-source tool for verifying fault-resistance in Verilog gate-level netlists.

- We extensively evaluate our tool on realistic cryptographic circuits, demonstrating

its effectiveness and efficiency.

**Outline**. Section 2 briefly recaps circuits, fault injection attacks and their countermeasures. Section 3 formulates the fault-resistance verification problem, studies its computational complexity, and introduces an illustrating example. Section 4 presents our SAT-based verification approach. Section 5 reports experimental results. We discuss related work in Section 6 and finally conclude this work in Section 7.

To foster further research, benchmarks, experimental data and the source code of our tool are released at

https://github.com/S3L-official/FIRMER.

### 2 Preliminary

#### 2.1 Notations

We denote by  $\mathbb{B}$  the Boolean domain  $\{0,1\}$  and by [n] the set of integers  $\{1,\cdots,n\}$  for an integer  $n\geq 1$ . To describe standard circuits, we consider the logic gates: and  $(\land)$ , or  $(\lor)$ , nand  $(\overline{\land})$ , nor  $(\overline{\lor})$ , xor  $(\oplus)$ , xnor  $(\overline{\oplus})$ , and not  $(\neg)$ , all of which are binary gates except for not. Note that  $\overline{\bullet}(x_1,x_2) = \neg \bullet (x_1,x_2)$ , so  $\overline{\bullet}$  may be used to denote  $\bullet$  for  $\bullet \in \{\land,\lor,\oplus\}$ . In addition, we introduce three auxiliary logic gates to describe faulty circuits: nnot  $(\overline{\neg})$ , set  $(\Box)$  and reset  $(\Box)$ , where  $\overline{\neg}x = x$ ,  $\Box$  and  $\Box$  are two constant logic gates whose outputs are 1 and 0, respectively.

#### 2.2 Synchronous Circuits

We first introduce combinational circuits based on which we define synchronous circuits.

**Definition 1** (Combinational circuit). A combinational circuit C is a tuple

$$(V, I, O, E, \mathsf{g}),$$

where

- V is a finite set of vertices,  $I \subset V$  is a set of inputs, and  $O \subset V$  is a set of outputs;

- $E \subseteq (V \setminus O) \times (V \setminus I)$  is a set of edges each of which represents a wire connecting two vertices and carrying a digital signal from the domain  $\mathbb{B}$ ;

- (V, E) forms a directed acyclic graph (DAG);

- each internal vertex  $v \in V \setminus (I \cup O)$  is a logic gate associated with its function, given by g(v), whose fan-in size is equal to the in-degree of the vertex v.

Intuitively, a combinational circuit represents a Boolean function. The behavior of a combinational circuit is memoryless, namely, the outputs depend solely on the inputs and are independent of the circuit's past history. The semantics of the combinational circuit C is described by the associated Boolean function  $[\![C]\!]:\mathbb{B}^{|I|}\to\mathbb{B}^{|O|}$  such that for any signals  $\vec{x}\in\mathbb{B}^{|I|}$  of the inputs I,  $[\![C]\!](\vec{x})=\vec{y}$  iff under the input signals  $\vec{x}$  the output signals O of the circuit C are  $\vec{y}$ .

A (synchronous) sequential circuit is a combinational circuit with feedback synchronized by a global clock. It has primary inputs, primary outputs, a combinational circuit and memory in the form of registers (or flip-flops). The output signals of registers at a clock cycle represent an internal state. At each clock cycle, the combinational circuit produces its output using the current internal state and the primary inputs as its inputs. The output comprises two parts: one is used as primary output while the other is stored in the registers, which will be the internal state for the next clock cycle and can be seen as the feedback of the combinational circuit to the next clock cycle.

We focus on round-based circuit implementations of cryptographic primitives so that the synchronous circuits always have bounded clock cycles and can be automatically unrolled by clock cycles. However, in theory, our methodology is generic and our approach may be adapted to handle other architectures with bounded clock cycles. The details are left as future work.

**Definition 2** (Synchronous circuit). A k-clock cycle synchronous (sequential) circuit S for  $k \geq 1$  is a tuple

$$(\mathcal{I}, \mathcal{O}, \mathcal{R}, \vec{s}_0, \mathcal{C}),$$

where

- $\mathcal{I}$  (resp.  $\mathcal{O}$ ) is a finite set of primary inputs (resp. primary outputs);

- $\mathcal{R} = R_0 \uplus \cdots \uplus R_k$  is a set of registers, called *memory gates*;

- $\vec{s}_0 \in \mathbb{B}^{|R_0|}$  gives initial signals to the memory gates in  $R_0$ ;

- $C = \{C_1, \dots, C_k\}$  where  $C_i = (V_i, I_i, O_i, E_i, \mathsf{g}_i)$  for each  $i \in [k]$  is a combinational circuit. Moreover, the inputs  $I_i$  are only connected from the primary inputs and memory gates  $R_{i-1}$ , the outputs  $O_i$  are only connected to the primary outputs and memory gates  $R_i$ , and  $V_i \cap V_j = \emptyset$  for any  $j \neq i$ .

Since memory gates are used for synchronization only and are essentially the same as the identity function, for the sake of presentation, we extend the function  $g_i$  such that for every memory gate  $r \in R_{i-1}$ ,  $g_i(r) = \overline{\ }$ . However, we emphasize that it may be changed if fault injections are considered.

A state  $\vec{s}$  of the circuit S comprises the output signals of the memory gates. At any clock cycle  $i \in [k-1]$ , given a state  $\vec{s}_{i-1}$  and signals  $\vec{x}_i$  of the primary inputs  $\mathcal{I}$ , the next state  $\vec{s}_i$  is  $[\![C_i]\!](\vec{s}_{i-1},\vec{x})$  projected onto the registers  $R_i$  and  $[\![C_i]\!](\vec{s}_{i-1},\vec{x})$  projected onto  $\mathcal{O}$  gives the primary outputs  $\vec{y}_i$ . In general, we write  $\vec{s}_{i-1} \xrightarrow{\vec{x}_i \mid \vec{y}_i} \vec{s}_i$  for the state transition at the i-th clock cycle.

A run  $\pi$  under a given sequence of primary inputs  $(\vec{x}_1, \dots, \vec{x}_k)$  is a sequence

$$\vec{s_0} \xrightarrow{\vec{x_1}|\vec{y_1}} \vec{s_1} \xrightarrow{\vec{x_2}|\vec{y_2}} \vec{s_2} \xrightarrow{\vec{x_3}|\vec{y_3}} \vec{s_3} \cdots \vec{s_{k-1}} \xrightarrow{\vec{x_k}|\vec{y_k}} \vec{s_k}.$$

The *semantics* of the circuit  $\mathcal{S}$  is described by its associated Boolean function

$$\llbracket \mathcal{S} \rrbracket : (\mathbb{B}^{|\mathcal{I}|})^k \to (\mathbb{B}^{|\mathcal{O}|})^k$$

such that for any sequence of input signals  $\vec{x}_1, \dots, \vec{x}_k \in (\mathbb{B}^{|\mathcal{I}|})^k$ , the following condition holds:

$$\llbracket \mathcal{S} \rrbracket (\vec{x}_1, \cdots, \vec{x}_k) = (\vec{y}_1, \cdots, \vec{y}_k) \text{ iff } \vec{s}_0 \overset{\vec{x}_1 | \vec{y}_1}{\longrightarrow} \vec{s}_1 \overset{\vec{x}_2 | \vec{y}_2}{\longrightarrow} \vec{s}_2 \overset{\vec{x}_3 | \vec{y}_3}{\longrightarrow} \vec{s}_3 \cdots \vec{s}_{k-1} \overset{\vec{x}_k | \vec{y}_k}{\longrightarrow} \vec{s}_k.$$

Given an output  $o \in \mathcal{O}$ , we define  $[\![\mathcal{S}]\!]_{\downarrow o}$  as a function such that for any sequence of input signals  $\vec{x}_1, \cdots, \vec{x}_k \in (\mathbb{B}^{|\mathcal{I}|})^k$ ,  $[\![\mathcal{S}]\!]_{\downarrow o}(\vec{x}_1, \cdots, \vec{x}_k)$  is the signal of the output o at the k-th clock cycle. Given a clock cycle  $i \in [k]$ , we denote by  $\mathcal{S}_i$  the sub-circuit of the circuit  $\mathcal{S}$  in which all the combinational circuits  $C_j$  for j > i are removed. Thus, for any sequence of input signals  $\vec{x}_1, \cdots, \vec{x}_k \in (\mathbb{B}^{|\mathcal{I}|})^k$  such that  $[\![\mathcal{S}]\!](\vec{x}_1, \cdots, \vec{x}_k) = (\vec{y}_1, \cdots, \vec{y}_k)$ , we have:  $[\![\mathcal{S}_i]\!](\vec{x}_1, \cdots, \vec{x}_i) = (\vec{y}_1, \cdots, \vec{y}_i)$ . Furthermore,  $[\![\mathcal{S}_i]\!]_{\downarrow o}(\vec{x}_1, \cdots, \vec{x}_i)$  is the signal of the output o of the circuits  $\mathcal{S}_i$  and  $\mathcal{S}$  at the i-th clock cycle.

We remark that in practice, the combinational circuits  $C_i$ 's in round-based hardware implementations of a cryptographic primitive are often similar (many of them are actually the same up to renaming of the vertices), because the internal rounds of a cryptographic primitive often perform similar computations. Furthermore, only partial signals of primary inputs  $\mathcal{I}$  may be used in one clock cycle and only the signals of primary outputs  $\mathcal{O}$  produced in the last clock cycle may be useful for the circuit functionality (in which case the signals of primary outputs  $\mathcal{O}$  in the other clock cycles are useless for the circuit functionality). Our formalization is designed to be general.

### 2.3 Fault Injection Attacks

Fault injection attacks are a type of physical attacks that actively inject faults on some logic and/or memory gates during the execution of a cryptographic circuit and then statistically analyze the faulty primary outputs to deduce sensitive data such as the cryptographic key [Bak22]. Over the last two decades, various fault injection mechanisms have been proposed such as clock glitches [ADN<sup>+</sup>10, ESH<sup>+</sup>11, SHO19], underpowering [SGD08], voltage glitches [ZDCT13], electromagnetic pulses [DDRT12, DLM19, DLM21], and laser beams [SA03, RSDT13, CLFT14, SFG<sup>+</sup>16, DBC<sup>+</sup>18].

Clock glitch causes transient faults in circuits by tampering with a clock signal with glitches. Under the normal clock, the clock cycle is larger than the maximum path delay in combinational circuits, allowing full propagation of the signals so that the input signals to memory gates are stable before the next clock signal triggers the sampling process of the memory gates. In contrast, under a clock with glitches, some clock periods are shorter than the maximum path delay so the input signals to memory gates become unstable (i.e., only parts of input signals have reached). As a result, the memory gates may sample faulty results.

Underpowering and voltage glitches are similar to clock glitches except that underpowering lowers the supply voltage of the device throughout an entire execution while voltage glitches only lower the supply voltage for a limited period of time during an execution. In contrast to clock glitches that decrease clock periods, lowering supply voltage increases the maximum path delay in combinatorial circuits which also induces memory gates to sample faulty results.

Electromagnetic pulses induce currents in wire loops that are power and ground networks in integrated circuits. The induced current in a wire loop leads to a (negative or positive) voltage swings between the power and ground grid. A negative (resp. positive) voltage swings decreases (resp. increases) the clock and input signals to memory gates,

often leading to reset (resp. set) of the corresponding memory gates, thus injecting faults on memory gates. A laser beam on a transistor produces a dense distribution of electron-hole pairs along the laser path, leading to a reduced voltage and eventually a temporary drift current. The temporary drift current can be used to alter the output signal of a (logic or memory) gate.

Clock glitches, underpowering and voltage glitches are non-invasive, as they do not require a modification of the targeted device, thus are considered as rather inexpensive. In contrast, electromagnetic pulses and laser beams are semi-invasive, allowing the adversary to inject localized faults, thus have higher precision than non-invasive attacks, but still at reasonable equipment and expertise requirement.

#### 2.4 Countermeasures

Various countermeasures have been proposed to defend against fault injection attacks. For clock glitches, underpowering and voltage glitches, an alternative implementation of the circuit can be developed where signal path delays in combinatorial circuits are made independent of the sensitive data. For instance, delay components can be added to certain signal paths [GAS14, ELH<sup>+</sup>15], or combinational circuits can be reorganized [EWW16], so that the arrival time of all output signals of logic gates are independent of the sensitive data. However, such countermeasures fail to defend against electromagnetic pulses and laser beams.

Redundancy-based countermeasures are proposed to detect the presence of a fault. For instance, spatial redundancy recomputes the output multiple times in parallel [MSY06]; temporal redundancy recomputes the output multiple times consecutively [MSY06], and information redundancy leverages linear error code from coding theory [AMR<sup>+</sup>20]. Once a fault is detected, the output is omitted or the sensitive data is destroyed, with an error flag signal. However, such countermeasures are still vulnerable against advanced fault injection attacks such as Ineffective Fault Attack (IFA) [Cla07b] and Statistical Ineffective Fault Analysis (SIFA) [DEK<sup>+</sup>18]. The linear error-code based approach proposed in [AMR<sup>+</sup>20] was extended in [SRM20], which can correct faults to protect against IFA and SIFA.

In this work, we are interested in verifying redundancy based countermeasures including detection- and correction-based ones [MSY06, AMR<sup>+</sup>20, SRM20]. We do not consider countermeasures that make the arrival time of all output signals of logic gates independent of the sensitive data [GAS14, ELH<sup>+</sup>15], as they fail to defend against more advanced fault injection attacks.

#### 3 The Fault-Resistance Verification Problem

In this section, inspired by the consolidated fault model [RBSG23], we first formalize the fault-resistance verification problem, and then present an illustrating example.

#### 3.1 Problem Formulation

Fix a k-clock cycle circuit  $\mathcal{S} = (\mathcal{I}, \mathcal{O}, \mathcal{R}, \vec{s_0}, \mathcal{C})$ , where  $\mathcal{C} = \{C_1, \cdots, C_k\}$  and  $C_i = (V_i, I_i, O_i, E_i, \mathsf{g}_i)$  for each  $i \in [k]$ . We assume that  $\mathcal{S}$  is a cryptographic circuit without deploying any countermeasures. Let  $\mathcal{S}' = (\mathcal{I}, \mathcal{O}', \mathcal{R}', \vec{s_0}, \mathcal{C}')$  be the protected counterpart of  $\mathcal{S}$  using a detection-based or correction-based countermeasure [MSY06, AMR<sup>+</sup>20, SRM20], where  $\mathcal{C}' = \{C_1', \cdots, C_k'\}$  and  $C_i' = (V_i', I_i', O_i', E_i', \mathbf{g}_i')$  for each  $i \in [k]$ . We assume that  $\mathcal{O}' = \mathcal{O} \cup \{o_{\mathtt{flag}}\}$ , where  $o_{\mathtt{flag}}$  is an error flag output indicating whether a fault was detected when the circuit  $\mathcal{S}'$  adopts a detection-based countermeasure, i.e., no error flag output is involved, for clarity, we assume that the error flag output  $o_{\mathtt{flag}}$  is added but is always 0.

To formalize the fault-resistance verification problem, we first introduce some notations. We denote by **B** the blacklist of gates that are protected against fault injection attacks. Note that the blacklist  $\mathbf{B}$  is configurable which may be empty as in [RBSS<sup>+</sup>21]. It usually contains the gates used in the sub-circuits implementing a detection or correction mechanism, otherwise, the adversary can directly inject faults into them. It can be seen as a set of minimal vulnerable gates that should be protected. Note that the effects of faults injected on the other gates can be propagated into the gates in **B**.

To model the effects of different fault injections, we introduce the following three fault types:

- bit-set fault  $\tau_s$ : when injected on a gate, its output becomes 1;

- bit-reset fault  $\tau_r$ : when injected on a gate, its output becomes 0;

- bit-flip fault  $\tau_{bf}$ : when injected on a gate, its output is flipped, i.e., either from 1 to 0 or from 0 to 1.

These fault types are able to capture all the effects of faults induced by both noninvasive fault injections (i.e., clock glitches, underpowering and voltage glitches) and semi-invasive fault injections (i.e., electromagnetic pulses and laser beams). We refer readers to [RBSG23] for the detailed discussion. We denote by  $\mathcal{T} = \{\tau_s, \tau_r, \tau_{bf}\}$  the set of

A fault injection with fault type  $\tau \in \mathcal{T}$  on a gate can be exactly characterized by replacing its associated function  $\bullet$  with  $\tau(\bullet)$ , where

$$\tau(\bullet) := \left\{ \begin{array}{ll} \sqcap, & \text{if } \tau = \tau_s; \\ \sqcup, & \text{if } \tau = \tau_r; \\ \overline{\bullet}, & \text{if } \tau = \tau_{bf}. \end{array} \right.$$

To specify when, where and how a fault is injected, we introduce fault events.

**Definition 3** (Fault event). A fault event is given by  $e(\sigma, \beta, \tau)$ , where

- $\sigma \in [k]$  specifies the clock cycle of the fault injection, namely, the fault injection occurs at the  $\sigma$ -th clock cycle;

- $\beta \in R'_{\sigma-1} \cup V'_{\sigma} \setminus (I'_{\sigma} \cup O'_{\sigma})$  specifies the gate on which the fault is injected; we require

- $\tau \in \mathcal{T}$  specifies the fault type of the fault injection.

A fault event  $e(\sigma, \beta, \tau)$  yields the faulty circuit  $S'[e(\sigma, \beta, \tau)] = (\mathcal{I}, \mathcal{O}', \mathcal{R}', \vec{s}'_0, \mathcal{C}'')$ , where  $\mathcal{C}'' = \{C_1'', \cdots, C_k''\}, \text{ for each } i \in [k] \text{ and every } \beta' \in R_{\sigma-1}' \cup V_{\sigma}' \setminus (I_{\sigma}' \cup O_{\sigma}'),$

$$\begin{split} \bullet & \ C_i'' := \left\{ \begin{array}{ll} (V_i', I_i', O_i', E_i'', \mathbf{g}_i''), & \text{if } i = \sigma; \\ C_i', & \text{if } i \neq \sigma; \end{array} \right. \\ \bullet & \ \mathbf{g}_\sigma''(\beta') := \left\{ \begin{array}{ll} \tau(\mathbf{g}_\sigma'(\beta)), & \text{if } \beta' = \beta; \\ \mathbf{g}_\sigma'(\beta), & \text{if } \beta' \neq \beta, \end{array} \right. \\ \bullet & \ E_i'' \text{ is obtained from } E_i' \text{ by removing the incoming edges of } \beta \text{ if } \tau \in \{\tau_s, \tau_r\}. \end{split}$$

Intuitively, the faulty circuit  $\mathcal{S}'[e(\sigma,\beta,\tau)]$  is the same as the circuit  $\mathcal{S}'$  except that the function  $g'_{\sigma}(\beta)$  of the gate  $\beta$  is transiently replaced by  $\tau(g'_{\sigma}(\beta))$  in the  $\sigma$ -th clock cycle, while all the other gates at all the clock cycles remain the same. We denote by  $\tau(\beta)$  the faulty counterpart of the gate  $\beta$  with fault type  $\tau$ .

In practice, multiple fault events can occur simultaneously during the same clock cycle and/or consecutively in different clock cycles, allowing the adversary to conduct sophisticated fault injection attacks. To formalize this, we introduce fault vectors, as a generalization of fault events.

**Definition 4** (Fault vector). A fault vector  $V(S', \mathbf{B}, T)$  is given by a (non-empty) set of fault events

$$V(\mathcal{S}', \mathbf{B}, T) := \left\{ \begin{array}{l} \mathsf{e}(\alpha_1, \beta_1, \tau_1), \cdots, \mathsf{e}(\alpha_m, \beta_m, \tau_m) & | & \forall i, j \in [m]. \alpha_i \in [k] \land \tau_i \in T \land \\ (i \neq j \land \alpha_i = \alpha_j \implies \beta_i \neq \beta_j) \end{array} \right\}.$$

A fault can be injected to a gate at most once in the circuit  $\mathcal{S}'$ , but multiple faults can be injected to different gates, in the same or different clock cycles. Note that  $\mathcal{S}'$  is unrolled with clock cycles where each physical gate in the original circuit is renamed in different clock cycles. As a result, different gates in a fault vector may correspond to the same physical gate in the original circuit, allowing us to capture persistent and permanent faults (called multi-cycle faults hereafter) using fault vectors.

For instance, consider a physical gate  $\beta \notin \mathbf{B}$  in the original circuit. The unrolled counterpart  $\mathcal{S}'$  consists of k versions  $\{\beta_1, \dots, \beta_k\}$  of the physical gate  $\beta$ , where the gate  $\beta_k$  denotes the physical gate  $\beta$  in the k-th clock cycle of the original circuit. A d-cycle fault on the physical gate  $\beta$  with fault type  $\tau$  is captured by the set of fault vectors  $\{V_{\alpha}(\mathcal{S}', \mathbf{B}, \{\tau\}) \mid 0 \leq \alpha < k\}$ , where the fault vector  $V_{\alpha}(\mathcal{S}', \mathbf{B}, \{\tau\})$  is defined as

$$\mathsf{V}_{\alpha}(\mathcal{S}',\mathbf{B},\{\tau\}) = \big\{\mathsf{e}(\alpha+1,\beta_{\alpha+1},\tau),\cdots,\mathsf{e}(\alpha+d',\beta_{\alpha+d'},\tau)\mid d' = \min(d,k-\alpha)\big\}.$$

A fault vector  $V(S', \mathbf{B}, T)$  on the circuit S' yields the faulty circuit  $S'[V(S', \mathbf{B}, T)]$ , which is obtained by iteratively applying fault events in  $V(S', \mathbf{B}, T)$ , i.e.,

$$\mathcal{S}'[\mathsf{V}(\mathcal{S}',\mathbf{B},T)] := \mathcal{S}'[\mathsf{e}(\alpha_1,\beta_1,\tau_1)] \cdots [\mathsf{e}(\alpha_m,\beta_m,\tau_m)].$$

**Definition 5** (Effectiveness of fault vectors). A fault vector  $V(S', \mathbf{B}, T)$  is *effective* if there exists a sequence of primary inputs  $(\vec{x}_1, \dots, \vec{x}_k)$  such that the sequences of primary outputs  $[S'](\vec{x}_1, \dots, \vec{x}_k)$  and  $[S'[V(S', \mathbf{B}, T)]](\vec{x}_1, \dots, \vec{x}_k)$  differ at some clock cycle which is before the clock cycle when the error flag output  $o_{flag}$  differs.

Intuitively, an effective fault vector breaks the functional equivalence between S and S' and the fault is *not* successfully detected (i.e., setting the error flag output  $o_{\text{flag}}$ ). Note that there are two possible cases for an ineffective fault vector: either  $[S'](\vec{x}_1, \dots, \vec{x}_k)$  and  $[S'[V(S', \mathbf{B}, T)]](\vec{x}_1, \dots, \vec{x}_k)$  are the same for each sequence of primary inputs  $(\vec{x}_1, \dots, \vec{x}_k)$  or the fault is successfully detected in time.

Hereafter,  $\sharp \mathtt{Clk}(\mathsf{V}(\mathcal{S}',\mathbf{B},T))$  denotes the cardinality of the set  $\{\alpha_1,\cdots,\alpha_m\}$ , i.e., the number of clock cycles when fault events can occur, and by  $\mathtt{MaxFEpClk}(\mathsf{V}(\mathcal{S}',\mathbf{B},T))$  the maximum number of fault events per clock cycle, i.e.,  $\max_{\alpha\in[k]}|\{e(\alpha,\beta,\tau)\in\mathsf{V}(\mathcal{S}',\mathbf{B},T)\}|$ . Inspired by the consolidated fault model [RBSG23], we introduce the security model of fault-resistance which characterizes the capabilities of the adversary.

**Definition 6** (Fault-resistance model). A fault-resistance model is given by  $\zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$ , where

- $n_e$  is the maximum number of fault events per clock cycle;

- $\mathbf{n}_c$  is the maximum number of clock cycles in which fault events can occur;

- $T \subseteq \mathcal{T}$  specifies the allowed fault types; and

- $\ell \in \{1, m, lm\}$  defines vulnerable gates: 1 for logic gates in combinational circuits, m for memory gates and lm for both logic and memory gates.

For instance, the fault-resistance model  $\zeta(\mathbf{n}_e,k,\mathcal{T}, \mathtt{lm})$  gives the strongest capability to the adversary for a large  $\mathbf{n}_e$  allowing the adversary to inject faults to all the gates simultaneously at any clock cycle (except for those protected in the blacklist  $\mathbf{B}$ ). The fault-resistance model  $\zeta(1,1,\{\tau_{bf}\},1)$  only allows the adversary to choose one logic gate to inject a bit-flip fault in one chosen clock cycle. Formally,  $\zeta(\mathbf{n}_e,\mathbf{n}_c,T,\ell)$  defines the set  $[\![\zeta(\mathbf{n}_e,\mathbf{n}_c,T,\ell)]\!]$  of possible fault vectors that can be conducted by the adversary, i.e.,  $[\![\zeta(\mathbf{n}_e,\mathbf{n}_c,T,\ell)]\!]$  is

$$\{\mathsf{V}(\mathcal{S}',\mathbf{B}_\ell,T)\mid \mathtt{MaxFEpClk}(\mathsf{V}(\mathcal{S}',\mathbf{B}_\ell,T))\leq n_e \wedge \sharp \mathtt{Clk}(\mathsf{V}(\mathcal{S}',\mathbf{B}_\ell,T))\leq \mathtt{n}_c,\}$$

$$\text{where } \mathbf{B}_{\ell} := \left\{ \begin{array}{ll} \mathbf{B}, & \text{if } \ell = \mathtt{lm}; \\ \mathbf{B} \cup \mathcal{R}, & \text{if } \ell = \mathtt{l}; \\ \mathbf{B} \cup \bigcup_{i \in [k]} V_i' \setminus (I_i' \cup O_i'), & \text{if } \ell = \mathtt{m}. \end{array} \right.$$

The circuit S' is fault-resistant w.r.t. a blacklist **B** and a fault-resistance model  $\zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$ , denoted by  $\langle \mathcal{S}', \mathbf{B} \rangle \models \zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$ , if all the fault vectors  $\mathsf{V}(\mathcal{S}', \mathbf{B}, T) \in$  $[\![\zeta(\mathbf{n}_e,\mathbf{n}_c,T,\ell)]\!]$  are ineffective on the circuit  $\mathcal{S}'$ .

**Definition 7** (Fault-resistance verification problem). The fault-resistance verification problem is to determine if  $\langle \mathcal{S}', \mathbf{B} \rangle \models \zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$ , and in particular, if  $\langle \mathcal{S}', \mathbf{B} \rangle \models$  $\zeta(\mathbf{n}_e,\mathbf{n}_c,\mathcal{T},\mathtt{lm}).$

The definition of our fault-resistance covers all the feasible fault vectors  $V(S', \mathbf{B}, T) \in$  $[(\zeta(n_e, n_c, T, \ell))]$ , allowing us to verify fault-resistance against both multi-cycle faults and random faults by choosing proper values for the parameters  $n_e$  and  $n_c$ . For instance, it suffices to set  $\mathbf{n}_e = n \cdot \min(d, m)$  and  $\mathbf{n}_c = \max(m \cdot d, k)$  for n number of d-cycle (random) faults per clock cycle in at most m clock cycles for  $m \leq k$  (i.e., up to  $n \cdot m$  number d-cycle faults in total).

**Proposition 1.** If  $\langle \mathcal{S}', \mathbf{B} \rangle \models \zeta(\mathbf{n}_e, \mathbf{n}_c, \mathcal{T}, \mathbf{lm})$ , then  $\langle \mathcal{S}', \mathbf{B} \rangle \models \zeta(\mathbf{n}_e, \mathbf{n}_c, \mathcal{T}, \ell)$  for any  $T \subseteq \mathcal{T}$ and any  $\ell \in \{1, m, lm\}$ .

**Theorem 1.** The problem of determining whether a circuit S' is fault-resistant is coNPcomplete.

*Proof.* We show that the problem of determining whether a circuit S' is not fault-resistant is NP-complete.

To show that this problem is in NP, for a given fault-resistance model  $\zeta(n_e, n_c, T, \ell)$ , we first non-deterministically guess a sequence of primary inputs  $(\vec{x}_1, \dots, \vec{x}_k)$  and a fault vector  $V(S', \mathbf{B}, T) \in [\![\zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)]\!]$ , then construct the faulty circuit  $S'[V(S', \mathbf{B}, T)]$  in polynomial time by traversing and manipulating gates in the circuit  $\mathcal{S}'$ , and finally check if the sequences of primary outputs  $[S'](\vec{x}_1,\dots,\vec{x}_k)$  and  $[S'[V(S',\mathbf{B},T)]](\vec{x}_1,\dots,\vec{x}_k)$ differ at some clock cycle before the error flag output  $o_{\mathtt{flag}}$  differs in polynomial time by explicitly computing the sequences of primary outputs using the sequence of primary inputs  $(\vec{x}_1, \dots, \vec{x}_k)$ . If yes, then  $\langle \mathcal{S}', \mathbf{B} \rangle \not\models \zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$ .

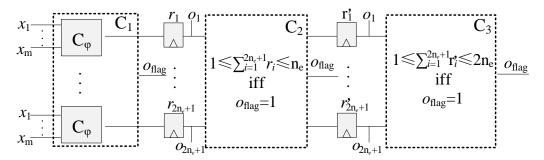

The NP-hardness is shown by reducing from the SAT problem<sup>2</sup>. Let  $C_{\varphi}$  be a combinational circuit representing a Boolean formula  $\varphi$ , where the inputs of  $C_{\varphi}$  are the Boolean variables of  $\varphi$  (say  $x_1, \dots, x_m$ ), and the output indicates the result of  $\varphi$ . We create a circuit  $S' = (\mathcal{I}, \mathcal{O}, \mathcal{R}, \vec{s}_0, \mathcal{C})$  as shown in Fig. 1, where

- $\mathcal{I} = \{x_1, \dots, x_m\}$  is the set of inputs of the circuit  $C_{\varphi}$ ;

- $\mathcal{O}$  is the set  $\{o_i, o_{\mathtt{flag}} \mid 1 \leq i \leq 2\mathtt{n}_e + 1\}$ ;  $\mathcal{R} = R_1 \cup R_2$ , with  $R_1 = \{r_i \mid 1 \leq i \leq 2\mathtt{n}_e + 1\}$  and  $R_2 = \{r_i' \mid 1 \leq i \leq 2\mathtt{n}_e + 1\}$ ;

- $\vec{s}_0$  is a vector consisting of 0;

- $C = \{C_1, C_2, C_3\}, \text{ such that }$

- $C_1$  comprises  $2n_e + 1$  copies of the circuit  $C_{\varphi}$ : all the copies share the same inputs  $\mathcal{I}$ , the output of the *i*-th copy is connected to  $r_i$ , and the output  $o_{flag}$  is always 0;

- $C_2$  outputs signals of the memory gates  $R_1$  and stores them into the memory gates  $R_2$  again, checks if  $1 \leq \sum_{i=1}^{2n_e+1} r_i \leq n_e$ , and the output  $o_{\text{flag}}$  is 1 iff  $1 \leq \sum_{i=1}^{2n_e+1} r_i \leq n_e$ ;

$C_3$  checks whether  $1 \leq \sum_{i=1}^{2n_e+1} r_i' \leq 2n_e$ , and the output  $o_{\text{flag}}$  is 1 iff  $1 \leq \sum_{i=1}^{2n_e+1} r_i' \leq 2n_e$ .

<sup>&</sup>lt;sup>2</sup>A Boolean formula is satisfiable iff there is an assignment of the variables under which the formula evaluates to true. The SAT problem is to determine whether a Boolean formula is satisfiable or not.

**Figure 1:** The circuit S' for NP-hardness.

**Table 1:** Truth table of the S-box in the block cipher RECTANGLE.

| $\vec{x}$                                                                     | 0000 | 0001 | 0010 | 0011 | 0100         | 0101 | 0110                  | 0111                  | 1000         | 1001 | 1010         | 1011         | 1100 | 1101 | 1110 | 1111 |

|-------------------------------------------------------------------------------|------|------|------|------|--------------|------|-----------------------|-----------------------|--------------|------|--------------|--------------|------|------|------|------|

| $S(\vec{x})$                                                                  | 0110 | 0101 | 1100 | 1010 | 0001         | 1110 | 0111                  | 1001                  | 1011         | 0000 | 0011         | 1101         | 1000 | 1111 | 0100 | 0010 |

| $S[s7, \tau_s](\vec{x})$ $S[s7, \tau_r](\vec{x})$ $S[s7, \tau_{bf}](\vec{x})$ | 0110 | 0101 | 1100 | 1010 | <b>1</b> 001 | 1110 | 0111                  | <b>0</b> 001          | <b>0</b> 011 | 0000 | <b>1</b> 011 | 1101         | 1000 | 1111 | 0100 | 0010 |

| $S[s9, 	au_s](ec{x})$<br>$S[s9, 	au_r](ec{x})$<br>$S[s9, 	au_{bf}](ec{x})$    | 0110 | 0000 | 1100 | 1010 | 000 <b>0</b> | 1110 | 0 <b>0</b> 1 <b>0</b> | 1 <b>1</b> 0 <b>0</b> | 1 <b>110</b> | 0000 | 001 <b>0</b> | 110 <b>0</b> | 1000 | 1110 | 0100 | 0010 |

**Claim.** The circuit S' is not fault-resistant w.r.t. the blacklist  $\mathbf{B} = \emptyset$  and the fault-resistance model  $\zeta(\mathbf{n}_e, 1, \{\tau_{bf}\}, \mathbf{m})$  iff the Boolean formula  $\varphi$  is satisfiable.

( $\Leftarrow$ ) Suppose  $\varphi$  is satisfiable. Let  $\vec{x}$  be the satisfying assignment of  $\varphi$ . Obviously, under the primary inputs  $\vec{x}$ , the output  $o_{\mathtt{flag}}$  is 0 and the outputs  $\{o_i \mid 1 \leq i \leq 2\mathtt{n}_e + 1\}$  are 1 in all the clock cycles. Consider the fault event  $\mathtt{e}(2, r_1, \tau_{bf})$ . Along the sequence of primary outputs  $[S'[\mathtt{e}(2, r_1, \tau_{bf})]](\vec{x})$ , the output  $o_{\mathtt{flag}}$  is 0 at the first two clock cycles and becomes 1 at the 3-rd clock cycle. However, the output  $o_1$  differs in  $[S'](\vec{x})$  and  $[S'[\mathtt{e}(2, r_1, \tau_{bf})]](\vec{x})$  at the 2nd clock cycle due to the bit-flip fault injection on the memory gate  $r_1$ . Thus,  $\langle S', \emptyset \rangle \not\models \zeta(\mathtt{n}_e, 1, \{\tau_{bf}\}, \mathtt{m})$ , i.e., the circuit S' is not fault-resistant w.r.t. the blacklist  $\mathbf{B} = \emptyset$  and the fault-resistance model  $\zeta(\mathtt{n}_e, 1, \{\tau_{bf}\}, \mathtt{m})$ .

(⇒) Suppose  $\varphi$  is unsatisfiable. Obviously, under any primary inputs  $\vec{x}$ , all the primary outputs  $\{o_{flag}, o_i \mid 1 \leq i \leq 2n_e + 1\}$  are 0 in all the clock cycles. For any fault vector  $V(S', \mathbf{B}, T) \in [\![\zeta(n_e, 1, \{\tau_{bf}\}, m)]\!]$ , at most  $n_e$  memory gates can be bit-flipped in one single clock cycle. If some memory gates in  $R_1$  are bit-flipped at the 2nd clock cycle, then the output  $o_{flag}$  is 1 at the 2nd clock cycle, successfully detecting the fault injection. If no memory gates of  $R_1$  are bit-flipped at the 2nd clock cycle and some memory gates in  $R_2$  are bit-flipped at the 3rd clock cycle, the primary outputs  $\{o_i \mid 1 \leq i \leq 2n_e + 1\}$  are 0 at the 2nd clock cycle,  $o_{flag}$  is 1 at the 3rd clock cycle successfully detecting the fault injection, although some primary outputs of  $\{o_i \mid 1 \leq i \leq 2n_e + 1\}$  become 1 at the 3rd clock cycle. Hence  $\langle S', \emptyset \rangle \models \zeta(n_e, 1, \{\tau_{bf}\}, m)$ , i.e., the circuit S' is fault-resistant w.r.t. the blacklist  $\mathbf{B} = \emptyset$  and the fault-resistance model  $\zeta(n_e, 1, \{\tau_{bf}\}, m)$ .

### 3.2 An Illustrating Example

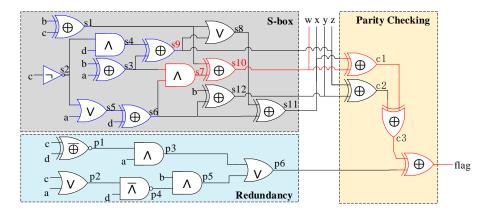

Consider the S-box used in the cipher RECTANGLE [ZBL<sup>+</sup>15], which is a 4-bit to 4-bit mapping  $S: \mathbb{B}^4 \to \mathbb{B}^4$  given in Table 1 (the top two rows). It can be implemented in a combinational circuit as shown in Fig. 2 (grey-area). It has four 1-bit inputs  $\{a, b, c, d\}$  denoting the binary representation of the 4-bit input  $\vec{x}$ , and four 1-bit outputs  $\{w, x, y, z\}$  denoting the binary representation of the 4-bit output  $S(\vec{x})$ , where a and w are the most

**Figure 2:** Circuit representation of the illustrating example.

```

1 RECTANGLE S-box

10

s6

s5 ⊕

рЗ

a \wedge p1

2 Input: a,b,c,d

11

s3

∧ s6

19

p2 \overline{\wedge} d

p4 ∧ b

V z

3 Output: w,x,y,z,flag

s8

20

12

s 1

s1 = b \oplus c

13

s1

\oplus

21

рЗ

⊕ s6

s2

s8

22

w \oplus x

14

c1

6

s3

= b ⊕ a

15

⊕ s6

23

c2 =

y \oplus z

\texttt{s2} \ \land \ \texttt{d}

s4

\overline{\oplus}

24

с3

c1 ⊕ c2

16

С

d

p1

s2 V

= c3 ⊕ p6

s5

25

a

17

p2

s3 \oplus s4

```

**Figure 3:** Pseudo-code of the illustrating example.

significant bits. The values of the inputs a,b,c and d depend upon the secret key. The corresponding pseudo-code of the illustrating example is given in Fig. 3, where the left two columns implements the function of the S-box and the right column implements a single-bit parity protection mechanism.

If a fault with fault type  $\tau$  is injected on the gate \$7 (i.e., the gate whose output is \$7), its function g(s7) is changed from  $\wedge$  to  $\tau(\wedge)$ . As highlighted in red color in Fig. 2, the effect of this fault will be propagated to the output w. We denote by  $S[s7,\tau]$  the faulty S-box, given in Table 1 for each  $\tau \in \mathcal{T}$ , where the faulty output is highlighted in **bold**. Since the distribution of the XOR-difference  $S[s7,\tau](\vec{x}) \oplus S(\vec{x})$  is biased, the adversary can narrow down the solutions for  $\vec{x}$  according to the value of  $S[s7,\tau](\vec{x}) \oplus S(\vec{x})$  which is known to the adversary. Finally, the adversary solves  $\vec{x}$  uniquely, based on which a round key can be obtained (Details refer to [Bak22]).

To thwart single-bit fault injection attacks, one may adopt a single-bit parity protection mechanism [KKG03, BBK<sup>+</sup>03], as shown in Fig. 2. The sub-circuit in the blue-area is a redundancy part which computes the Hamming weight of the output of the S-box from the input but independent on the sub-circuit in the grey-area, i.e., p6. The sub-circuit in the yellow-area checks the parity of the Hamming weights of  $S(\vec{x})$  computed in two independent sub-circuits, i.e.,  $flag = p6 \oplus w \oplus x \oplus y \oplus z$ . If no faults occur, flag is 0.

Re-consider the fault injected on the gate s7. We can see that either flag becomes 1, i.e., this fault injection can be successfully detected, or the outputs of  $S[s7, \tau](\vec{x})$  and  $S(\vec{x})$  are the same, thus the fault injection is ineffective.

However, the entire circuit is still vulnerable against single-bit fault injection attacks, as one single-bit fault injection can yield an even number of faulty output bits so that the Hamming weight of the faulty output remains the same. For instance, the fault injection on the gate  ${\tt s9}$  will affect both the outputs  ${\tt x}$  and  ${\tt z}$ . As shown in Table 1, the fault injection cannot be successfully detected if one of the following items holds:

```

• \tau = \tau_s \wedge \vec{x} \in \{0000, 1001, 1110, 1111\},\

```

Figure 4: Circuit representation of the revised illustrating example.

```

• \tau = \tau_r \wedge \vec{x} \in \{0001, 0110, 0111, 1000\},

• \tau = \tau_{bf} \wedge \vec{x} \in \{0000, 0001, 0110, 0111, 1000, 1001, 1110, 1111\}.

```

It is fault-resistant against single-bit fault injection attacks when the blacklist  $\bf B$  includes all the logic gates in the parity checking (i.e., yellow-area) and all the logic gates in the S-box (i.e., grey-area) whose out-degree is larger than 2 (highlighted in blue color in Fig. 2). This issue also could be avoided by leveraging the independence property defined by [AMR<sup>+</sup>20], to ensure an n-bit fault injection attack only affects at most n output bits, at the cost of the circuit size.

```

1 RECTANGLE S-box

14 \text{ s11} = \text{b} \oplus \text{c}

y = s17 \oplus s18

27

2 Input: a,b,c,d

15

s12 = s10 V

s11

28

s12 \oplus b

3 Output: w,x,y,z,flag

16

s13 =

29

s1 = ¬ c

17

s14 =

s13

30

5

s2 = a \oplus b

s15

d

p3 =

31

s3 =

6

\mathtt{b} \; \oplus \; \mathtt{c}

s16

19

32

d \wedge

7

s4 =

s1 \ a

20

s17

s16

р4

33

р5

s5

s4

p3 V

\oplus d

34

p6

9

s6 = s2 \wedge s5

s19

22

С

35

c1

\mathbf{w} \oplus \mathbf{x}

10

s7 = ¬ c

23

s20

a V

s19

36

c2 =

y ⊕ z

11

s8 = a \oplus b

s21

d \oplus s20

c3 =

37

c1 \oplus c2

s9 = s7 \wedge d

25

s3 ⊕ s6

12

13 s10 = s8 \oplus s9

26

```

**Figure 5:** Pseudo-code of the revised illustrating example.

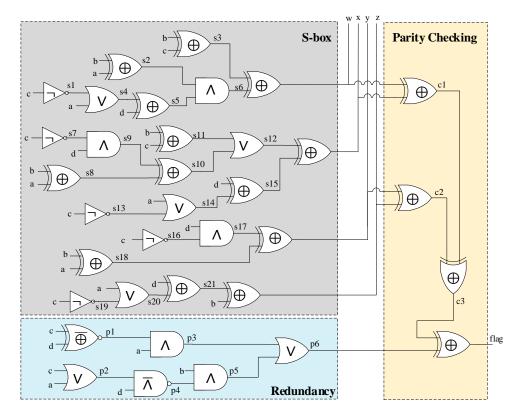

**Revised implementation.** The circuit representation of the revised implementation of the RECTANGLE S-box is shown in Fig. 4 and its pseudo-code is shown in Fig. 5,

following the independence property defined by [AMR<sup>+</sup>20].

This circuit is fault-resistant against single-bit fault injection attacks when the blacklist **B** includes *only* the logic gates in the parity checking. We can observe that any fault injection on one single logic gate in the redundancy part does not change any of the outputs  $\{w, x, y, z\}$ , any fault injection on one single logic gate in the S-box part only change one of the outputs  $\{w, x, y, z\}$  and also changes the error flag output flag. Thus, the revised implementation is fault-resistant w.r.t. the blacklist **B** and the fault-resistance model  $\zeta(1,1,\mathcal{T},1)$ , where **B** only contains the logic gates in the parity checking.

### 4 SAT-based Formal Verification

We propose an SAT-based countermeasure verification approach, which reduces the fault-resistance verification problems to SAT solving.

#### 4.1 Overview

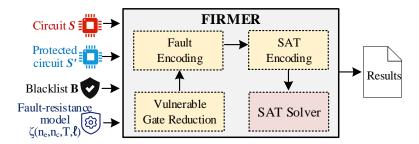

An overview of our approach is depicted in Fig. 6. Given a circuit  $\mathcal{S}$  (without any countermeasures), a protected circuit  $\mathcal{S}'$  (i.e.,  $\mathcal{S}$  with a countermeasure), a blacklist  $\mathbf{B}$  of gates on which faults cannot be injected, and a fault-resistance model  $\zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$ , FIRMER outputs a report on whether the circuit  $\mathcal{S}'$  is fault-resistant.

**Figure 6:** Framework of our verification approach.

FIRMER consists of three key components: vulnerable gate reduction, fault encoding and SAT encoding. The vulnerable gate reduction safely reduces the number of vulnerable gates, thus reducing the size of the resulting Boolean formulas and improving efficiency. The fault encoding replaces each vulnerable gate with a gadget (i.e., sub-circuit) with additional primary inputs controlling whether a fault is injected and selecting a fault type. The SAT encoding is an extension of the one for checking functional equivalence, where (i) the maximum number of fault events per clock cycle and the maximum number of clock cycles in which fault events can occur are both expressed by constraints over control inputs, and (ii) a constraint on the error flag output is added.

Below, we present the details of our fault encoding method, SAT encoding method and vulnerable gate reduction

#### 4.2 Fault Encoding

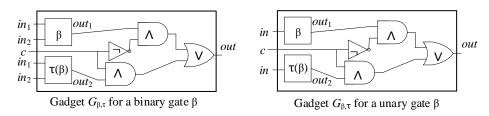

**Gadgets.** To encode a fault injection on a gate  $\beta$  with fault type  $\tau \in \mathcal{T}$  and gate function  $g(\beta) = \bullet$ , we define a gadget  $G_{\beta,\tau}$  shown in Fig. 7. Note that  $\tau(\beta)$  denotes the faulty counterpart of the gate  $\beta$  w.r.t. the fault type  $\tau$ , i.e.,  $g(\tau(\beta)) = \tau(\bullet)$ . Indeed, the gadget  $G_{\beta,\tau}$  for a binary gate  $\beta$  defines a Boolean formula  $\llbracket G_{\beta,\tau} \rrbracket$  with

$$[G_{\beta,\tau}](in_1, in_2, c) = c ? (in_1 \diamond in_2) : (in_1 \bullet in_2),$$

**Figure 7:** Gadgets for encoding one fault type.

where  $\diamond = \tau(\bullet)$ , and c is a *control input* indicating whether a fault is injected or not. Namely,  $G_{\beta,\tau}$  is equivalent to the faulty gate  $\tau(\beta)$  if c=1, otherwise  $G_{\beta,\tau}$  is equivalent to the original gate  $\beta$ . Note that the incoming edges of  $\tau(\beta)$  should be omitted if  $\tau \in \{\tau_s, \tau_r\}$ . The gadget  $G_{\beta,\tau}$  for a unary gate  $\beta$  is defined similarly as:

$$\llbracket G_{\beta,\tau} \rrbracket (in,c) = c ? (\diamond in) : (\bullet in).$$

We now generalize the gadget definition to accommodate different fault types  $\mathcal{T} = \{\tau_s, \tau_r, \tau_{bf}\}$ . Besides a control input c, selection inputs  $(b_1, b_2)$  are introduced to choose fault types. The gadget  $G_{\beta,\mathcal{T}}$  for a binary logic gate  $\beta$  defines a Boolean formula  $\llbracket G_{\beta,\mathcal{T}} \rrbracket$  such that

$$[\![G_{\beta,\mathcal{T}}]\!](in_1,in_2,c,b_1,b_2) = c ? (b_1?(b_2?(in_1\diamond in_2):(in_1\dagger in_2)):(in_1\ddagger in_2)):(in_1\ddagger in_2)) : (in_1 \ddagger in_$$

- c = 0 means that no fault is injected, i.e.,  $G_{\beta,\mathcal{T}}$  is equivalent to the gate  $\beta$ ;

- c=1 means that a fault is injected. Moreover, the selection inputs  $(b_1,b_2)$  are defined as:

- if  $b_1 = b_2 = 1$ , then  $G_{\beta,\mathcal{T}}$  becomes the faulty logic gate  $\tau_s(\beta)$ ;

- if  $b_1 = 1$  and  $b_2 = 0$ , then  $G_{\beta,\mathcal{T}}$  becomes the faulty logic gate  $\tau_r(\beta)$ ;

- if  $b_1 = 0$ , then  $G_{\beta,\mathcal{T}}$  becomes to the faulty logic gate  $\tau_{bf}(\beta)$ ;

The gadget  $G_{\beta,\mathcal{T}}$  for a unary gate  $\beta$  can be defined as the Boolean formula  $\llbracket G_{\beta,\mathcal{T}} \rrbracket$  such that

$$[G_{\beta,\mathcal{T}}](in,c,b_1,b_2) = c? (b_1? (b_2? (\diamond in): (\dagger in)): (\dagger in)): (\bullet in).$$

For a subset of fault types  $T = \{\tau_1, \tau_2\} \subset \mathcal{T}$ , the gadget  $G_{\beta,T}$  for a binary or unary gate  $\beta$  can be defined accordingly such that

$$\llbracket G_{\beta,T} \rrbracket (in_1,in_2,c,b) = c ? \left( b ? (in_1 \diamond in_2) : (in_1 \dagger in_2) \right) : (in_1 \bullet in_2), \\ \llbracket G_{\beta,T} \rrbracket (in,c,b) = c ? \left( b ? (\diamond in) : (\dagger in) \right) : (\bullet in),$$

```

where \diamond = \tau_1(\bullet) and \dagger = \tau_2(\bullet).

```

We remark that the faulty counterpart  $\tau(\beta)$  of a register  $\beta$  is implemented by adding a logic gate so that no additional registers are introduced. More specifically,  $\tau_s(\beta)$  (resp.  $\tau_r(\beta)$ ) is a constant logic gate that always outputs the signal 1 (resp. 0), and  $\tau_{bf}(\beta)$  is a not logic gate with the incoming edge from the output of the register  $\beta$ .

Conditionally-controlled faulty circuits. From the protected circuit S', we construct a conditionally-controlled faulty circuit S'', where each vulnerable gate is replaced by a gadget defined above.

Fix a fault-resistance model  $\zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$ . Assume that the control input c and the set of selection inputs of each gadget  $G_{\beta,T}$  are distinct and different from the ones used

in the circuit  $\mathcal{S}'$ . We define the conditionally-controlled faulty circuit  $\mathcal{S}''$  w.r.t.  $\mathbf{B}$  and  $\zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$  as

$$\mathcal{S}'[\mathbf{B}, \zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)] := (\mathcal{I} \uplus \mathcal{I}', \mathcal{O}', \mathcal{R}', \vec{s}'_0, \mathcal{C}''),$$

where  $\mathcal{I}' = \bigcup_{i \in [k]} I_i''$  and  $\mathcal{C}'' = \{C_1'', \cdots, C_k''\}$ . For every  $i \in [k]$ , the circuit  $C_i'' = (V_i' \uplus V_i'', I_i' \uplus I_i'', O_i', E_i' \uplus E_i'', g_i'')$  is obtained from the combinational circuit  $C'_i$  as follows:

For every gate  $\beta \in R'_{i-1} \cup V'_i \setminus (I'_i \cup O'_i)$ , if  $\beta \notin \mathbf{B}_\ell$ , then  $\beta$  is replaced by the gadget  $G_{\beta,T}$ , the control and selection inputs of the gadget  $G_{\beta,T}$  are added into  $I_i''$ , the gates and edges of  $G_{\beta,T}$  are added into  $V_i''$  and  $E_i''$  respectively, the mapping  $g_i'$  is expanded to  $g_i''$  accordingly.

Intuitively, a fault vector  $V(S', \mathbf{B}, T) \in [\![\zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)]\!]$  is encoded as a sequence  $(\vec{b}_1, \dots, \vec{b}_k)$  of the primary inputs  $\mathcal{I}'$  for controlling fault types such that  $\mathbf{e}(\alpha, \beta, \tau) \in$  $V(S', \mathbf{B}, T)$  iff the gadget  $G_{\beta,T}$  is equivalent to the faulty gate  $\tau(\beta)$  under the primary inputs  $\vec{b}_{\alpha}$ , i.e., the control input of  $G_{\beta,T}$  is 1 and the selection inputs of  $G_{\beta,T}$  choose  $\tau(\beta)$ . We note that if  $\mathbf{e}(\alpha, \beta, \tau) \notin \mathsf{V}(\mathcal{S}', \mathbf{B}, T)$  for any  $\tau \in T$ , then the gadget  $G_{\beta, T}$  is equivalent to the original gate  $\beta$  under the primary inputs  $\vec{b}_{\alpha}$ , i.e., the control input of the gadget  $G_{\beta,T}$  is the signal 0.

We say that a fault vector  $V(S', \mathbf{B}, T)$  and a sequence  $(\vec{b}_1, \dots, \vec{b}_k)$  of the primary inputs  $\mathcal{I}'$  are compatible if the sequence  $(\vec{b}_1, \dots, \vec{b}_k)$  encodes the fault vector  $\mathsf{V}(\mathcal{S}', \mathbf{B}, T)$ . Note that a sequence  $(\vec{b}_1, \dots, \vec{b}_k)$  of the primary inputs  $\mathcal{I}'$  determines a unique compatible fault vector  $V(S', \mathbf{B}, T)$ , but a fault vector  $V(S', \mathbf{B}, T)$  determines a unique compatible sequence  $(\vec{b}_1, \dots, \vec{b}_k)$  of the primary inputs  $\mathcal{I}'$  only if  $T \subset \mathcal{T}$ , because  $G_{\beta,\mathcal{T}}$  is equivalent to the faulty logic gate  $\tau_{bf}(\beta)$  if  $b_1 = 0$  no matter the value of  $b_2$ . Thus, we can get:

**Proposition 2.** The number of gates of the circuit S'' (i.e.,  $S'[\mathbf{B}, \zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)]$ ) is at most 6|T| times than that of the circuit S', and the following statements hold:

1. for each fault vector  $V(S', \mathbf{B}, T) \in [\![\zeta(n_e, n_c, T, \ell)]\!]$ , there exists a compatible sequence  $(\vec{b}_1, \dots, \vec{b}_k)$  of the primary inputs  $\mathcal{I}'$  such that for each sequence  $(\vec{x}_1, \dots, \vec{x}_k)$  of primary inputs  $\mathcal{I}$ ,

$$\llbracket \mathcal{S}'[\mathsf{V}(\mathcal{S}',\mathbf{B},T)] \rrbracket (\vec{x}_1,\cdots,\vec{x}_k) = \llbracket \mathcal{S}'' \rrbracket ((\vec{x}_1,\vec{b}_1),\cdots,(\vec{x}_k,\vec{b}_k));$$

2. for each sequence  $(\vec{b}_1, \dots, \vec{b}_k)$  of the primary inputs  $\mathcal{I}'$ , there exists a unique compatible fault vector  $V(S', \mathbf{B}, T) \in [\![\zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)]\!]$  such that for each sequence  $(\vec{x}_1, \dots, \vec{x}_k)$  of primary inputs  $\mathcal{I}$ ,

$$\llbracket \mathcal{S}'[\mathsf{V}(\mathcal{S}',\mathbf{B},T)] \rrbracket (\vec{x}_1,\cdots,\vec{x}_k) = \llbracket \mathcal{S}'' \rrbracket ((\vec{x}_1,\vec{b}_1),\cdots,(\vec{x}_k,\vec{b}_k)).$$

Hereafter, for any sequence  $(\vec{b}_1, \dots, \vec{b}_k)$  of the primary inputs  $\mathcal{I}'$ , we denote by  $\sharp \mathtt{Clk}(\vec{b}_1,\cdots,\vec{b}_k)$  the number of clock cycles i such that at least one control input of  $\vec{b}_i$  is 1, and by MaxFEpClk $(\vec{b}_1,\cdots,\vec{b}_k)$  the maximum sum of the control inputs of  $\vec{b}_i$  per clock cycle  $i \in [k]$ .

#### 4.3 SAT Encoding

Recall that  $\langle \mathcal{S}', \mathbf{B} \rangle \models \zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$  iff each fault vector  $\mathsf{V}(\mathcal{S}', \mathbf{B}, T) \in \llbracket \zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell) \rrbracket$  is ineffective, i.e., for any sequence  $(\vec{x}_1, \dots, \vec{x}_k)$  of primary inputs, either  $[S'](\vec{x}_1, \dots, \vec{x}_k)$  $[S'[V(S', \mathbf{B}, T)]](\vec{x}_1, \dots, \vec{x}_k)$  or the fault is successfully detected by setting the error flag output  $o_{\text{flag}}$  in time. By Proposition 2,  $\langle \mathcal{S}', \mathbf{B} \rangle \models \zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$  iff for any sequence  $((\vec{x}_1, \vec{b}_1), \cdots, (\vec{x}_k, \vec{b}_k))$  of primary inputs  $\mathcal{I} \cup \mathcal{I}'$  such that  $\sharp \mathtt{Clk}(\vec{b}_1, \cdots, \vec{b}_k) \leq \mathtt{n}_c$  and  $\mathtt{MaxFEpClk}(\vec{b}_1, \cdots, \vec{b}_k) \leq \mathtt{n}_e$ , either  $[\![\mathcal{S}']\!](\vec{x}_1, \cdots, \vec{x}_k) = [\![\mathcal{S}'']\!]((\vec{x}_1, \vec{b}_1), \cdots, (\vec{x}_k, \vec{b}_k))$  or the fault is successfully detected by setting the error flag output  $o_{\mathtt{flag}}$  in time.

The above conditions can be reduced to the SAT problem by adapting the SAT encoding for equivalence checking [KvE02, KH03], with two additional constraints:

$$\sharp \mathtt{Clk}(\vec{b}_1,\cdots,\vec{b}_k) \leq \mathtt{n}_c \text{ and } \mathtt{MaxFEpClk}(\vec{b}_1,\cdots,\vec{b}_k) \leq \mathtt{n}_c.$$

Formally, the fault-resistance problem of the circuit S' can be formulated as:

$$\begin{aligned} \forall \vec{x}_1, \cdots, \vec{x}_k \in \mathbb{B}^{|\mathcal{I}|}. \ \forall \vec{b}_1 \in \mathbb{B}^{|I_1''|}, \cdots, \forall \vec{b}_k \in \mathbb{B}^{|I_k''|}. \\ \forall i \in [k]. \ \forall o \in \mathcal{O} \setminus \{o_{\mathtt{flag}}\}. \\ \left( \sharp \mathtt{Clk}(\vec{b}_1, \cdots, \vec{b}_k) \leq \mathtt{n}_c \wedge \mathtt{MaxFEpClk}(\vec{b}_1, \cdots, \vec{b}_k) \leq \mathtt{n}_e \right) \\ \Rightarrow \left( \psi_{i,o} \neq \psi_{i,o}'' \Rightarrow \exists j \in [i]. \ \psi_{j,o_{\mathtt{flag}}}'' \right) \end{aligned}$$

where  $\psi_{i,o}$  is a Boolean formula that is satisfiable under an assignment  $(\vec{x}_1, \dots, \vec{x}_i)$  iff  $[\![S_i']\!]_{\downarrow o}(\vec{x}_1, \dots, \vec{x}_i) = 1$ , and  $\psi_{i,o}''$  is a Boolean formula that is satisfiable under an assignment  $((\vec{x}_1, \vec{b}_1), \dots, (\vec{x}_i, \vec{b}_i))$  iff  $[\![S_i'']\!]_{\downarrow o}((\vec{x}_1, \vec{b}_1), \dots, (\vec{x}_i, \vec{b}_i)) = 1$ . Note that  $[\![S_i']\!]_{\downarrow o}(\vec{x}_1, \dots, \vec{x}_i)$  (resp.  $[\![S_i'']\!]_{\downarrow o}((\vec{x}_1, \vec{b}_1), \dots, (\vec{x}_i, \vec{b}_i))$ ) denotes the signal of the output o of the circuit  $S_i'$  (resp.  $S_i''$ ) at the i-th clock cycle.

Intuitively, Eqn.1 is valid iff for any sequence  $((\vec{x}_1, \vec{b}_1), \cdots, (\vec{x}_k, \vec{b}_k))$  of primary inputs  $\mathcal{I} \cup \mathcal{I}'$  such that  $\sharp \mathtt{Clk}(\vec{b}_1, \cdots, \vec{b}_k) \leq \mathtt{n}_c$  and  $\mathtt{MaxFEpClk}(\vec{b}_1, \cdots, \vec{b}_k) \leq \mathtt{n}_e$ , if some primary output o (except for the error flag  $o_{\mathtt{flag}}$ ) differs at some clock cycle i, then the error flag  $o_{\mathtt{flag}}$  should be 1 at some clock cycle j with  $j \leq i$ , i.e., the fault injection is detected in time.

By negating the above formula, the fault-resistance verification problem is reduced to the satisfiability of the Boolean formula  $(\Psi_{fr})$ :

$$\begin{split} &\Psi_{fr} := \left( \begin{array}{c} \Psi_{\mathbf{n}_c} \wedge \Psi_{\mathbf{n}_e} \wedge \bigvee_{i \in [k]} \bigvee_{o \in \mathcal{O} \setminus \{o_{\mathtt{flag}}\}} \left( \psi_{i,o} \neq \psi_{i,o}'' \wedge \bigwedge_{j \in [i]} \neg \psi_{i,o_{\mathtt{flag}}}'' \right), \end{array} \right) \text{ where} \\ &\Psi_{\mathbf{n}_c} := \left( \bigwedge_{i \in [k]} (d_i \Leftrightarrow \bigvee \vec{b}_{i,ctrl}) \right) \wedge \sum_{i \in [k]} d_i \leq \mathbf{n}_c, \qquad \Psi_{\mathbf{n}_e} := \bigwedge_{i \in [k]} \left( \sum \vec{b}_{i,ctrl} \leq \mathbf{n}_e \right) \end{split}$$

and for each  $i \in [k]$ ,  $\vec{b}_{i,ctrl}$  denotes the set of control inputs in the primary inputs  $\vec{b}_i$ . Intuitively,  $\Psi_{\mathbf{n}_c}$  encodes the constraint  $\sharp \mathtt{Clk}(\vec{b}_1,\cdots,\vec{b}_k) \leq \mathbf{n}_c$ , where for each  $i \in [k]$ ,  $d_i$  is a fresh Boolean variable such that  $d_i$  is 1 iff some control input in  $\vec{b}_{i,ctrl}$  is 1. Thus,  $\sum_{i \in [k]} d_i$  is the total number of clock cycles during which at least one fault is injected on some gate.  $\Psi_{\mathbf{n}_c}$  encodes the constraint  $\mathtt{MaxFEpClk}(\vec{b}_1,\cdots,\vec{b}_k) \leq \mathbf{n}_e$ , where for each  $i \in [k]$ ,  $\sum \vec{b}_{i,ctrl}$  is the total number of faults injected at the i-th clock cycle.

Though cardinality constraints of the form  $\sum_{i \in [n]} b_i \leq k$  are used in both  $\Psi_{\mathbf{n}_c}$  and  $\Psi_{\mathbf{n}_c}$ , they can be efficiently translated into Boolean formulas in polynomial time, and the size of the resulting Boolean formula is also polynomial in the size of the cardinality constraint [ES06, Wyn18]. In our implementation, we use the sorting network implemented in Z3 [dMB08] for translating cardinality constraints into Boolean formulas.

**Proposition 3.**  $\langle \mathcal{S}', \mathbf{B} \rangle \models \zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$  iff the formula  $\Psi_{fr}$  is unsatisfiable, where the size of  $\Psi_{fr}$  is polynomial in the size of the circuit  $\mathcal{S}'$ .

**Example 1.** Consider the fault-resistance model  $\zeta(1,1,\mathcal{T},1)$ . Suppose S is the circuit in Fig. 2 (grey-area), S' is the entire circuit in Fig. 2, and the blacklist  $\mathbf{B}$  contains all the logic gates in the redundancy and parity checking parts. The Boolean formula  $\Psi_{fr}$  of the example is

$$\Psi_{fr} := \Psi_{\mathbf{n}_c} \wedge \Psi_{\mathbf{n}_e} \wedge \big(\bigvee_{o \in \{\mathbf{w}, \mathbf{x}, \mathbf{y}, \mathbf{z}\}} \psi_{1,o} \neq \psi_{1,o}''\big) \wedge \neg \psi_{1, \mathtt{flag}}'' \bigwedge_{i=1}^{12} \phi_i$$

where

```

\begin{array}{lll} \Psi_{\mathbf{n}_c} := \left(d_1 \Leftrightarrow \bigvee_{i=1}^{12} c_i\right) \wedge d_1 \leq 1 & \Psi_{\mathbf{n}_e} := \left(\sum_{i=1}^{12} c_i \leq 1\right) \\ \psi_{1,\mathbf{x}} := \left((b \oplus c) \vee (b \oplus a \oplus (\neg c \wedge d))\right) \oplus \left((\neg c \vee a) \oplus d\right) & \psi_{1,\mathbf{y}} := b \oplus (\neg c \vee a) \oplus d \\ \psi_{1,\mathbf{w}} := (b \oplus c) \oplus \left((b \oplus a) \wedge ((\neg c \vee a) \oplus d)\right) & \psi_{1,\mathbf{z}} := b \oplus a \oplus (\neg c \wedge d) \\ \phi_1 := g_1 \Leftrightarrow G''_{\oplus,\mathcal{T}}(b,c,c_1,b_{1,1},b_{1,2}) & \psi''_{1,\mathbf{w}} := g_{10} \\ \phi_2 := g_2 \Leftrightarrow G''_{\neg,\mathcal{T}}(c,c_2,b_{2,1},b_{2,2}) & \psi''_{1,\mathbf{y}} := g_{12} \\ \phi_3 := g_3 \Leftrightarrow G''_{\oplus,\mathcal{T}}(b,a,c_3,b_{3,1},b_{3,2}) & \psi''_{1,\mathbf{z}} := g_{11} \\ \phi_4 := g_4 \Leftrightarrow G''_{\wedge,\mathcal{T}}(g_2,d,c_4,b_{4,1},b_{4,2}) & \psi''_{1,\mathbf{z}} := g_{9} \\ \phi_5 := g_5 \Leftrightarrow G''_{\vee,\mathcal{T}}(g_2,a,c_5,b_{5,1},b_{5,2}) & \phi_6 := g_6 \Leftrightarrow G''_{\oplus,\mathcal{T}}(g_5,d,c_6,b_{6,1},b_{6,2}) \\ \phi_{10} := g_{10} \Leftrightarrow G''_{\oplus,\mathcal{T}}(g_1,g_7,c_{10},b_{10,1},b_{10,2}) & \phi_7 := g_7 \Leftrightarrow G''_{\wedge,\mathcal{T}}(g_3,g_6,c_7,b_{7,1},b_{7,2}) \\ \phi_{11} := g_{11} \Leftrightarrow G''_{\oplus,\mathcal{T}}(g_6,g_8,c_{11},b_{11,1},b_{11,2}) & \phi_8 := g_8 \Leftrightarrow G''_{\vee,\mathcal{T}}(g_1,g_9,c_8,b_{8,1},b_{8,2}) \\ \phi_{12} := g_{12} \Leftrightarrow G''_{\oplus,\mathcal{T}}(g_6,b,c_{12},b_{12,1},b_{12,2}) & \phi_9 := g_9 \Leftrightarrow G''_{\oplus,\mathcal{T}}(g_3,g_4,c_9,b_{9,1},b_{9,2}) \\ \psi''_{1,\mathbf{flag}} := g_9 \oplus g_{10} \oplus g_{11} \oplus g_{12} \oplus \left(\left(a \wedge (c\overline{\oplus}d)\right) \vee \left(\left((a \vee c)\overline{\wedge}d\right) \wedge b\right)\right). \end{array}

```

Note that  $g_i$  for each  $i \in [12]$  is a fresh Boolean variable as a shortcut of a common gadget via  $\phi_i$ ,  $b_{i,1}$  and  $b_{i,2}$  (resp.  $c_i$ ) for each  $i \in [12]$  are fresh Boolean variables denoting the selection inputs (resp. control input) of the corresponding gadget,  $\Psi_{\mathbf{n}_c}$  can be removed from  $\Psi_{fr}$  since it always holds, and  $\Psi_{\mathbf{n}_e}$  can be efficiently translated into an equivalent Boolean formula.

We can show that  $\Psi_{fr}$  is satisfiable, thus S' is not fault-resistant w.r.t. the blacklist  $\mathbf{B}$  and  $\zeta(1,1,\mathcal{T},1)$ . Note that in practice,  $\mathbf{B}$  only contains all the logic gates in the parity checking. For simplicity,  $\mathbf{B}$  also contains all the logic gates in the redundancy part in this example.

#### 4.4 Vulnerable Gate Reduction

Consider a fault event  $\mathbf{e}(\alpha, \beta, \tau)$  to the circuit  $\mathcal{S}'$ . For any fixed sequence of primary inputs  $(\vec{x}_1, \dots, \vec{x}_k)$ , if the output signal of the gate  $\beta$  does not change,  $\mathbf{e}(\alpha, \beta, \tau)$  will not affect the primary outputs and thus can be omitted; otherwise, the effect of  $\mathbf{e}(\alpha, \beta, \tau)$  must be propagated to the successor gates.

Assume the output of the gate  $\beta$  is *only* connected to one vulnerable logic gate  $\beta'$ . If the output signal of  $\beta'$  does not change, the effect of the fault event  $e(\alpha, \beta, \tau)$  terminates at  $\beta'$ , thus  $e(\alpha, \beta, \tau)$  can be omitted. If it changes, it is flipped either from 1 to 0 or from 0 to 1, the same effect can be achieved by applying the fault event  $e(\alpha, \beta', \tau_{bf})$ , or the fault event  $e(\alpha, \beta', \tau_s)$  if it is flipped from 0 to 1 or the fault event  $e(\alpha, \beta', \tau_r)$  if it is flipped from 1 to 0. As a result, it suffices to consider fault injections on the gate  $\beta'$  instead of both  $\beta$  and  $\beta'$  when  $\tau_{bf} \in T$  or  $\{\tau_s, \tau_r\} \subseteq T$ , which reduces the number of vulnerable gates.

**Theorem 2.** Consider a fault-resistance model  $\zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$  such that  $\tau_{bf} \in T$  or  $\{\tau_s, \tau_r\} \subseteq T$ , and  $\ell \in \{1, 1m\}$ . Let

$$\mathsf{V}_1(\mathcal{S}',\mathbf{B},T) = \mathsf{V}(\mathcal{S}',\mathbf{B},T) \cup \{\mathsf{e}(\alpha,\beta,\tau)\} \in [\![\zeta(\mathsf{n}_e,\mathsf{n}_c,T,\ell)]\!]$$

be an effective fault vector on the circuit S'. If the output of the gate  $\beta$  is only connected to one logic gate  $\beta'$  and  $\beta' \notin \mathbf{B}$ , then there exists a fault vector  $V'(S', \mathbf{B}, T) \subseteq V(S', \mathbf{B}, T) \cup \{e(\alpha, \beta', \tau')\}$  for some  $\tau' \in T$  such that  $V'(S', \mathbf{B}, T)$  is also effective on the circuit S'.

Moreover, if  $V(S', \mathbf{B}, T) = \emptyset$ , then  $\{e(\alpha, \beta', \tau')\}$  for some  $\tau' \in T$  is effective on the circuit S'.

*Proof.* Suppose  $V_1(S', \mathbf{B}, T)$  is an effective fault vector on S'. There exists a sequence of primary inputs  $(\vec{x}_1, \dots, \vec{x}_k)$  such that the sequence of primary outputs  $[S'](\vec{x}_1, \dots, \vec{x}_k)$  and  $[S'[V_1(S', \mathbf{B}, T)]](\vec{x}_1, \dots, \vec{x}_k)$  differ at some clock cycle before the error flag output  $o_{\mathsf{flag}}$  differs. We proceed by distinguishing whether the output signal of the gate  $\beta'$  differs in the circuits S' and  $S'[V_1(S', \mathbf{B}, T)]$  under the same sequence of primary inputs  $(\vec{x}_1, \dots, \vec{x}_k)$ .

- If the output signal of the gate  $\beta'$  is the same in the circuits  $\mathcal{S}'$  and  $\mathcal{S}'[\mathsf{V}_1(\mathcal{S}',\mathbf{B},T)]$  under the same sequence of primary inputs  $(\vec{x}_1,\cdots,\vec{x}_k)$ , then the effect of the fault event  $\mathsf{e}(\alpha,\beta,\tau)$  is stopped at the gate  $\beta'$ , as the output of the gate  $\beta$  is only connected to the gate  $\beta'$ . Thus, the sequences of primary outputs  $[\![\mathcal{S}'[\mathsf{V}(\mathcal{S}',\mathbf{B},T)]\!]](\vec{x}_1,\cdots,\vec{x}_k)$  and  $[\![\mathcal{S}'[\mathsf{V}(\mathcal{S}',\mathbf{B},T)]\!]](\vec{x}_1,\cdots,\vec{x}_k)$  are the same, implying that the sequences of primary outputs  $[\![\mathcal{S}'[\mathsf{V}(\mathcal{S}',\mathbf{B},T)]\!]](\vec{x}_1,\cdots,\vec{x}_k)$  and  $[\![\mathcal{S}']\!](\vec{x}_1,\cdots,\vec{x}_k)$  differ at some clock cycle before the error flag output  $o_{\mathsf{flag}}$  differs. The result follows immediately.

- If the output signal of the gate  $\beta'$  differs in the circuits  $\mathcal{S}'$  and  $\mathcal{S}'[\mathsf{V}_1(\mathcal{S}',\mathbf{B},T)]$  under the same sequence of primary inputs  $(\vec{x}_1,\cdots,\vec{x}_k)$ , then the fault propagation from the fault event  $\mathsf{e}(\alpha,\beta,\tau)$  flips the output signal of the gate  $\beta'$ . Let  $\mathsf{V}_2(\mathcal{S}',\mathbf{B},T) = \mathsf{V}(\mathcal{S}',\mathbf{B},T) \cup \{\mathsf{e}(\alpha,\beta',\tau')\}$ , where  $\tau' = \tau_{bf}$  if  $\tau_{bf} \in T$ , otherwise  $\tau = \tau_s$  if the output signal of the gate  $\beta'$  flips from 0 to 1 due to the fault event  $\mathsf{e}(\alpha,\beta,\tau)$  and  $\tau = \tau_r$  if the output signal of the gate  $\beta'$  flips from 1 to 0 due to the fault event  $\mathsf{e}(\alpha,\beta,\tau)$ . Then, the sequences of primary outputs  $[\![\mathcal{S}'[\mathsf{V}_1(\mathcal{S}',\mathbf{B},T)]\!]](\vec{x}_1,\cdots,\vec{x}_k)$  and  $[\![\mathcal{S}'[\mathsf{V}_2(\mathcal{S}',\mathbf{B},T)]\!]](\vec{x}_1,\cdots,\vec{x}_k)$  are the same, as the output of the gate  $\beta$  is only connected to the gate  $\beta'$ . Thus,  $[\![\mathcal{S}']\!](\vec{x}_1,\cdots,\vec{x}_k)$  and  $[\![\mathcal{S}'[\mathsf{V}_2(\mathcal{S}',\mathbf{B},T)]\!](\vec{x}_1,\cdots,\vec{x}_k)$  differ at some clock cycle before the error flag output  $o_{\mathsf{flag}}$  differs. The result follows immediately.

Moreover, if  $V(S', \mathbf{B}, T) = \emptyset$ , the output signal of the gate  $\beta'$  must differ in the circuits S' and  $S'[V_1(S', \mathbf{B}, T)]$  under the same sequence of primary inputs  $(\vec{x}_1, \dots, \vec{x}_k)$ , otherwise  $V_1(S', \mathbf{B}, T)$  is ineffective on the circuit S'. The result follows from the fact that  $V_2(S', \mathbf{B}, T) = \{e(\alpha, \beta', \tau')\}$ .

Let  $\mathbf{B}'$  be the set of gates  $\beta$  such that the output of  $\beta$  is only connected to one logic gate  $\beta' \notin \mathbf{B}$ , which can be computed by a graph traversal of the circuit  $\mathcal{S}'$ . By Theorem 2,  $\mathbf{B}'$  can be safely merged with the blacklist  $\mathbf{B}$  while no protections are required for those gates. Moreover,  $\langle \mathcal{S}', \mathbf{B} \rangle \models \zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$  entails  $\langle \mathcal{S}', \mathbf{B} \cup \mathbf{B}' \rangle \models \zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$ . We get that:

**Corollary 1.** Given a fault-resistance model  $\zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$  such that  $\tau_{bf} \in T$  or  $\{\tau_s, \tau_r\} \subseteq T$ , and  $\ell \in \{1, 1m\}$ ,  $\langle \mathcal{S}', \mathbf{B} \cup \mathbf{B}' \rangle \models \zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$  iff  $\langle \mathcal{S}', \mathbf{B} \rangle \models \zeta(\mathbf{n}_e, \mathbf{n}_c, T, \ell)$ .

We remark that the vulnerable gate reduction does not consider conditional fault propagation because the inputs of the gates are not fixed to constants 1/0 when considering all the valid inputs to the circuit. It could be adapted if some inputs of AND/OR gates are fixed.

Example 2. Consider the fault-resistance model  $\zeta(1,1,\mathcal{T},1)$ , the circuit S in Fig. 2 (grey-area), and the entire circuit S' in Fig. 2. All the gates in the redundancy part except for the gate p6 (i.e., the gate whose output is p6) can be added into  $\mathbf{B}'$ , as the effect of an effective fault injection on any of those gates can be achieved by at most one bit-flip fault injection on p6. Note that p6 itself cannot be added into  $\mathbf{B}'$  because the gate flag is in  $\mathbf{B}$ . Similarly, the gates s4,s5,s7,s8 in the grey-area can be added into  $\mathbf{B}'$ , but the other gates cannot as their outputs are connected to more than one gate or some outputs of  $\{\mathbf{w}, \mathbf{x}, \mathbf{y}, \mathbf{z}\}$ . Now, the fault-resistance verification problem w.r.t. the fault-resistance model  $\zeta(1,1,\mathcal{T},1)$  and the blacklist  $\mathbf{B}$  is reduced to SAT solving of the Boolean formula  $(\Psi''_{fr})$

$$\Psi_{fr}'' := \Psi_{\mathbf{n}_c}' \wedge \Psi_{\mathbf{n}_e}' \wedge \Big(\bigvee_{o \in \{\mathbf{w}, \mathbf{x}, \mathbf{y}, \mathbf{z}\}} \psi_{1,o} \neq \psi_{1,o}''\Big) \wedge \neg \psi_{1,\mathtt{flag}}'' \wedge \bigwedge_{i=1}^{12} \phi_i',$$

where  $\phi'_i := \phi_i$  for  $i \in Z = \{1, 2, 3, 6, 9, 10, 11, 12\}$ ,  $\phi'_4 := g_4 \Leftrightarrow g_2 \land d$ ,  $\phi'_5 := g_5 \Leftrightarrow g_2 \lor a$ ,  $\phi'_7 := g_7 \Leftrightarrow g_3 \land g_6$ ,  $\phi'_8 := g_8 \Leftrightarrow g_1 \land g_9$ ,  $\Psi'_{n_c} := (d_1 \Leftrightarrow \bigvee_{i \in Z} c_i) \land d_1 \leq 1$  and  $\Psi'_{n_e} := (\sum_{i \in Z} c_i \leq 1)$ .

**Table 2:** Benchmark statistics, where Ri denotes i rounds, bi denotes countermeasure for i-bit faults, and D (resp. C) denotes detection-(resp. correction-)based countermeasure.

| Name                           | #Clk | $ \mathbf{B} $ | #in               | #out     | #gate         | #and       | #nand       | #or       | #nor        | #xor               | #xnor       | #not       | #reg              |

|--------------------------------|------|----------------|-------------------|----------|---------------|------------|-------------|-----------|-------------|--------------------|-------------|------------|-------------------|

| AES-R1                         | 1    | 0              | 256               | 128      | 21201         | 464        | 7936        | 592       | 8480        | 464                | 560         | 2705       | 0                 |

| AES-R1-b1-D                    | 1    | 432            | 256               | 129      | 24864         | 576        | 9446        | 560       | 9705        | 828                | 852         | 2897       | 0                 |

| AES-R1-b2-D                    | 1    | 1055           | 256               | 129      | 34159         | 704        | 12698       | 833       | 13012       | 1440               | 1584        | 3888       | 0                 |

| AES-R2                         | 2    | 0              | 384               | 128      | 42112         | 928        | 15872       | 1184      | 16960       | 992                | 1056        | 4864       | 256               |

| AES-R2-b1-D                    | 2    | 865            | 384               | 129      | 50017         | 1152       | 18892       | 1121      | 19410       | 1656               | 1704        | 5794       | 288               |

| AES-R2-b2-D                    | 2    | 2111           | 384               | 129      | 68703         | 1408       | 25396       | 1667      | 26024       | 2880               | 3168        | 7776       | 384               |

| CRAFT-R1                       | 2    | 0              | 128               | 64       | 480           | 0          | 160         | 16        | 80          | 80                 | 32          | 48         | 64                |

| CRAFT-R1-b1-C                  | 2    | 192            | 128               | 64       | 3140          | 0          | 864         | 48        | 656         | 460                | 728         | 272        | 112               |